# MOS INTEGRATED CIRCUIT

# $\mu$ PD78P083(A)

## 8-BIT SINGLE-CHIP MICROCONTROLLER

#### **DESCRIPTION**

The  $\mu$ PD78P083(A) is a member of the  $\mu$ PD78083 Subseries of the 78K/0 Series products. Comparing with the  $\mu$ PD78P083 (standard), more strict quality assurance programs are applied to this product (called Special of the quality grade in NEC). The  $\mu$ PD78P083(A) uses one-time PROM instead of internal ROMs of the  $\mu$ PD78081(A) and  $\mu$ PD78082(A).

Because this device can be programmed by users, it is ideally suited for applications involving the evaluation of systems in development stages, small-scale production of many different products, and rapid development and time-to-market of a new product.

The details of functions are described in the user's manuals. Be sure to read the following manuals before designing.

μPD78083 Subseries User's Manual : U12176E 78K/0 Series User's Manual — Instructions : IEU-1372

#### **FEATURES**

- Pin-compatible with mask ROM version (except VPP pin)

- Internal PROM: 24 Kbytes Note

- μPD78P083CU(A), μPD78P083GB(A): One-time programmable (ideally suited for small-scale production)

- Internal high-speed RAM: 512 bytes Note

- Can be operated in the same supply voltage as the mask ROM version (VDD = 1.8 to 5.5 V)

- Corresponding to QTOP™ Microcontrollers (under planning)

**Note** The internal PROM and internal high-speed RAM capacities can be changed by setting the internal memory size switching register (IMS).

- **Remarks 1.** QTOP microcontroller is a general term for microcontrollers which incorporate one-time PROM and are totally supported by NEC's programming service (from programming to marking, screening and

- verification).

- 2. For the differences between PROM and Mask ROM versions, refer to **Chapter 1. DIFFERENCES BETWEEN THE**  $\mu$ PD78P083(A) AND MASK ROM VERSIONS.

The information in this document is subject to change without notice.

#### **ORDERING INFORMATION**

| Part Number                                 | Package                                | Internal ROM  |

|---------------------------------------------|----------------------------------------|---------------|

| μPD78P083CU(A)                              | 42-pin plastic shrink DIP (600 mil)    | One-Time PROM |

| μPD78P083GB(A)-3B4                          | 44-pin plastic QFP (10 $\times$ 10 mm) | One-Time PROM |

| $\mu$ PD78P083GB(A)-3BS-MTX <sup>Note</sup> | 44-pin plastic QFP (10 $\times$ 10 mm) | One-Time PROM |

Note Under planning

Caution  $\mu$ PD78P083GB(A) has two types of packages. (Refer to Chapter 7. PACKAGE DRAWINGS). Consult an NEC's sales representative for suppliable packages.

## **QUALITY GRADE**

| Part Number                                 | Package                                | Quality Grades |

|---------------------------------------------|----------------------------------------|----------------|

| μPD78P083CU(A)                              | 42-pin plastic shrink DIP (600 mil)    | Special        |

| μPD78P083GB(A)-3B4                          | 44-pin plastic QFP (10 $\times$ 10 mm) | Special        |

| $\mu$ PD78P083GB(A)-3BS-MTX <sup>Note</sup> | 44-pin plastic QFP (10 $\times$ 10 mm) | Special        |

Note Under planning

Please refer to "Quality grades on NEC Semiconductor Devices" (Document number C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

## Deferences between $\mu$ PD78P083(A) and $\mu$ PD78P083

| Product<br>Item | μPD78P083(A)                                                               | μPD78P083                                                                                                             |

|-----------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Quality Grade   | Special                                                                    | Standard                                                                                                              |

| Package         | 42-pin plastic shrink DIP (600 mil) 44-pin plastic QFP (10 $\times$ 10 mm) | 42-pin plastic shrink DIP (600 mil) 44-pin plastic QFP (10 × 10 mm) 42-pin ceramic shrink DIP (with window) (600 mil) |

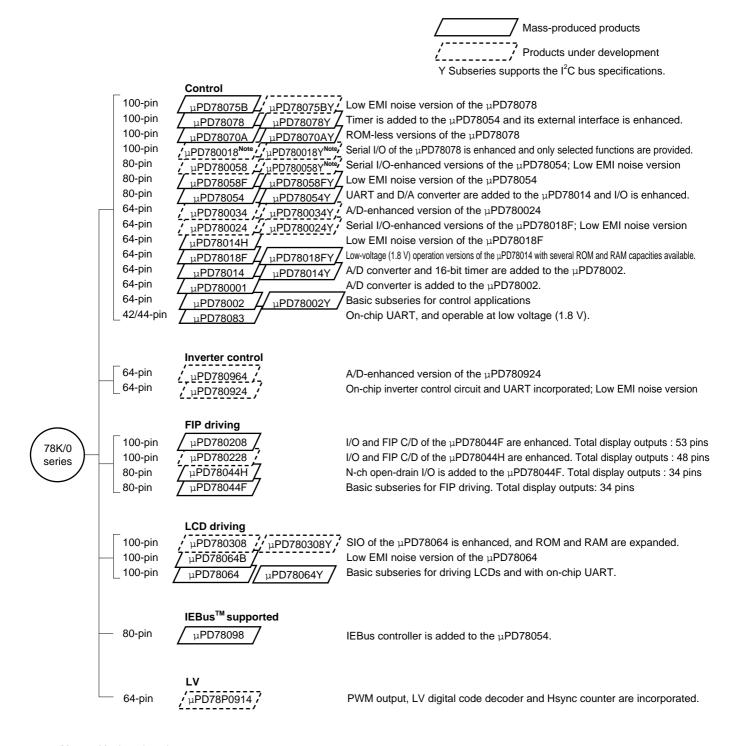

#### **78K/0 SERIES DEVELOPMENT**

The following shows the 78K/0 Series products development. Subseries names are shown inside frames.

Note Under planning

The following table shows the differences among subseries functions.

|                    | Function   | ROM        |       | Tir    | ner   |      | 8-bit | 10-bit | 8-bit | Serial interface                     | I/O | VDD MIN. | External  |

|--------------------|------------|------------|-------|--------|-------|------|-------|--------|-------|--------------------------------------|-----|----------|-----------|

| Subseries r        | name       | capacity   | 8-bit | 16-bit | Watch | WDT  | A/D   | A/D    | D/A   | Serial interface                     | 1/0 | value    | expansion |

| Control            | μPD78075B  | 32K to 40K | 4 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      | 2 ch  | 3 ch (UART: 1 ch)                    | 88  | 1.8 V    | Available |

|                    | μPD78078   | 48K to 60K |       |        |       |      |       |        |       |                                      |     |          |           |

|                    | μPD78070A  | _          |       |        |       |      |       |        |       |                                      | 61  | 2.7 V    |           |

|                    | μPD780018  | 48K to 60K |       |        |       |      |       |        | -     | 2 ch (Time division<br>3-wire: 1 ch) | 88  |          |           |

|                    | μPD780058  | 24K to 60K | 2 ch  |        |       |      |       |        | 2 ch  | 3 ch (Time division<br>UART: 1 ch)   | 68  | 1.8 V    |           |

|                    | μPD78058F  | 48K to 60K |       |        |       |      |       |        |       | 3 ch (UART: 1 ch)                    | 69  | 2.7 V    | _         |

|                    | μPD78054   | 16K to 60K |       |        |       |      |       |        |       |                                      |     | 2.0 V    |           |

|                    | μPD780034  | 8K to 32K  |       |        |       |      | _     | 8 ch   |       | 3 ch (UART: 1 ch, Time               | 51  | 1.8 V    |           |

|                    | μPD780024  |            |       |        |       |      | 8 ch  | _      |       | division 3-wire: 1 ch)               |     |          |           |

|                    | μPD78014H  |            |       |        |       |      |       |        |       | 2 ch                                 | 53  |          |           |

|                    | μPD78018F  | 8K to 60K  |       |        |       |      |       |        |       |                                      |     |          |           |

|                    | μPD78014   | 8K to 32K  |       |        |       |      |       |        |       |                                      |     | 2.7 V    |           |

|                    | μPD780001  | 8K         |       | _      | _     |      |       |        |       | 1 ch                                 | 39  |          | _         |

|                    | μPD78002   | 8K to 16K  |       |        | 1 ch  |      | _     |        |       |                                      | 53  |          | Available |

|                    | μPD78083   | _          |       |        | _     |      | 8 ch  |        |       | 1 ch (UART: 1 ch)                    | 33  | 1.8 V    | _         |

| Inverter           | μPD780964  | 8K to 32K  | 3 ch  | Note   | _     | 1 ch | _     | 8 ch   | _     | 2 ch (UART: 2 ch)                    | 47  | 2.7 V    | Available |

| control            | μPD780924  |            |       |        |       |      | 8 ch  | _      |       |                                      |     |          |           |

| FIP driving        | μPD780208  | 32K to 60K | 2 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      |       | 2 ch                                 | 74  | 2.7 V    | _         |

|                    | μPD780228  | 48K to 60K | 3 ch  | _      | _     |      |       |        |       | 1 ch                                 | 72  | 4.5 V    |           |

|                    | μPD78044H  | 32K to 48K | 2 ch  | 1 ch   | 1 ch  |      |       |        |       |                                      | 68  | 2.7 V    |           |

|                    | μPD78044F  | 16K to 40K |       |        |       |      |       |        |       | 2 ch                                 |     |          |           |

| LCD<br>driving     | μPD780308  | 48K to 60K | 2 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      |       | 3 ch (Time division<br>UART: 1 ch)   | 57  | 2.0 V    | _         |

|                    | μPD78064B  | 32K        | ,     |        |       |      |       |        |       | 2 ch (UART: 1 ch)                    |     |          |           |

|                    | μPD78064   | 16K to 32K |       |        |       |      |       |        |       |                                      |     |          |           |

| IEBus<br>supported | μPD78098   | 32K to 60K | 2 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      | 2 ch  | 3 ch (UART: 1 ch)                    | 69  | 2.7 V    | Available |

| LV                 | μPD78P0914 | 32K        | 6 ch  | _      | _     | 1 ch | 8 ch  | _      | _     | 2 ch                                 | 54  | 4.5 V    | Available |

Note 10 bits timer: 1 channel

## **FUNCTION DESCRIPTION**

| Item                        |              | Function                                                                                                                                                                                    |  |  |

|-----------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Internal memory             |              | <ul> <li>PROM: 24 Kbytes Note</li> <li>RAM</li> <li>High-speed RAM: 512 bytes Note</li> </ul>                                                                                               |  |  |

| Memory space                |              | 64 Kbytes                                                                                                                                                                                   |  |  |

| General register            |              | 8 bits x 32 registers (8 bits x 8 registers x 4 banks)                                                                                                                                      |  |  |

| Instruction cycles          |              | Instruction execution time variable function is integrated. 0.4 $\mu$ s/0.8 $\mu$ s/1.6 $\mu$ s/3.2 $\mu$ s/6.4 $\mu$ s/12.8 $\mu$ s (@5.0-MHz operation with main system clock)            |  |  |

| Instruction set             |              | <ul> <li>16-bit operation</li> <li>Multiply/divide (8 bits x 8 bits, 16 bits ÷ 8 bits)</li> <li>Bit manipulation (set, reset, test, Boolean operation)</li> <li>BCD adjust, etc.</li> </ul> |  |  |

| I/O ports                   |              | Total : 33                                                                                                                                                                                  |  |  |

| A/D converter               |              | 8-bit resolution x 8 channels                                                                                                                                                               |  |  |

| Serial interface            |              | 3-wired serial I/O/UART mode selectable: 1 channel                                                                                                                                          |  |  |

| Timer                       |              | <ul><li>8-bit timer/event counter: 2 channels</li><li>Watchdog timer: 1 channel</li></ul>                                                                                                   |  |  |

| Timer output                |              | 2 pins (8-bit PWM output enable)                                                                                                                                                            |  |  |

| Clock output                |              | 19.5 kHz, 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz, 2.5 MHz, and 5.0 MHz (@ 5.0-MHz operation with main system clock)                                                        |  |  |

| Buzzer output               |              | 1.2 kHz, 2.4 kHz, 4.9 kHz, and 9.8 kHz<br>(@ 5.0-MHz operation with main system clock)                                                                                                      |  |  |

| Vectored-interrupt Maskable |              | Internal : 8 external : 3                                                                                                                                                                   |  |  |

| source                      | Non-maskable | Internal : 1                                                                                                                                                                                |  |  |

| Software                    |              | Internal : 1                                                                                                                                                                                |  |  |

| Power supply voltage        |              | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                              |  |  |

| Operating ambient temp      | erature      | $T_A = -40 \text{ to } +85^{\circ}\text{C}$                                                                                                                                                 |  |  |

| Packages                    |              | 42-pin plastic shrink DIP (600 mil)     44-pin plastic QFP (10 × 10 mm)                                                                                                                     |  |  |

**Note** Internal PROM and high-speed RAM capacities can be changed by setting the memory size switching register (IMS).

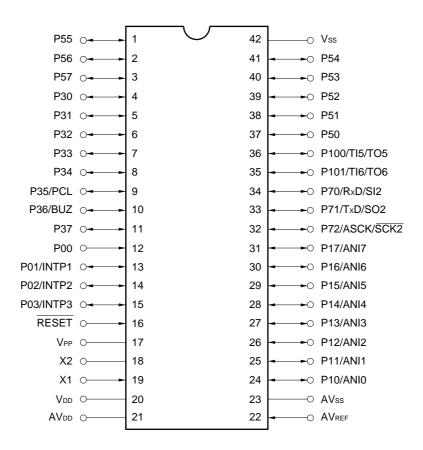

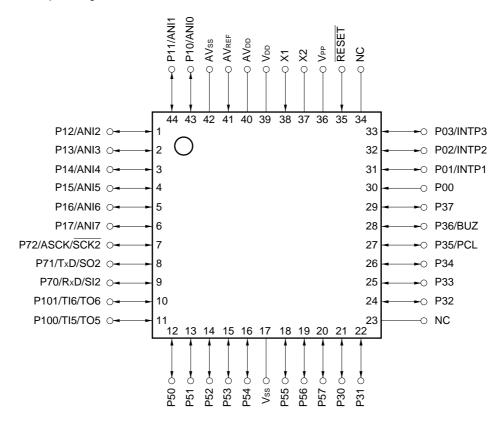

## PIN CONFIGURATIONS (Top View)

## (1) Normal operating mode

42-pin plastic shrink DIP (600 mil) μPD78P083CU(A)

Cautions 1. Connect VPP pin directly to Vss.

- 2. Connect AVDD pin to VDD.

- 3. Connect AVss pin to Vss.

44-pin plastic QFP (10 x 10 mm)

μPD78P083GB(A)-3B4, μPD78P083GB(A)-3BS-MTX<sup>Note</sup>

## Note Under planning

Cautions 1. Connect VPP pin directly to Vss.

- 2. Connect AVDD pin to VDD.

- 3. Connect AVss pin to Vss.

- 4. Connect NC pin to Vss for noise protection (It can be left open).

ANI0 to ANI7 : Analog Input PCL : Programmable Clock

ASCK : Asynchronous Serial Clock RESET : Reset

$AV_{DD}$ : Analog Power Supply RxD: Receive Data **AV**REF : Analog Reference Voltage SCK<sub>2</sub> : Serial Clock : Serial Input **AVss** : Analog Ground SI2 BUZ : Buzzer Clock SO<sub>2</sub> : Serial Output INTP1 to INTP3 : Interrupt from Peripherals TI5, TI6 : Timer Input NC : Non-connection TO5, TO6 : Timer Output

P30 to P37 : Port 3 VPP : Programming Power Supply

P50 to P57 : Port 5 Vss : Ground

P70 to P72 : Port 7 X1, X2 : Crystal (Main System Clock)

P100, P101 : Port 10

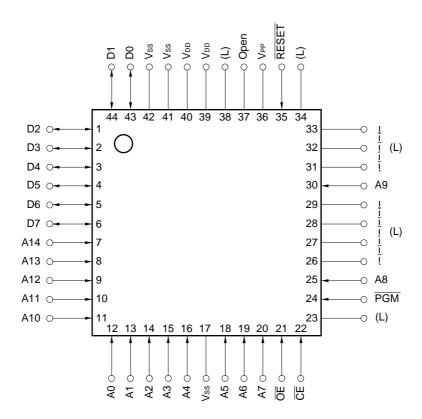

## (2) PROM programming mode

42-pin plastic shrink DIP (600 mil) μPD78P083CU(A)

Cautions 1. (L): Individually connect to Vss via a pull-down resistor.

Vss: Connect to GND.

RESET: Set to low level.

Open: Leave open.

44-pin plastic QFP (10 x 10 mm)

µPD78P083GB(A)-3B4, µPD78P083GB(A)-3BS-MTX<sup>Note</sup>

Note Under planning

Cautions 1. (L): Individually connect to Vss via a pull-down resistor.

Vss: Connect to GND.

RESET: Set to low level.

Open: Leave open.

A0 to A14 : Address Bus RESET : Reset

TE: Chip Enable VDD: Power Supply

D0 to D7 : Data Bus VPP : Programming Power Supply

OE : Output Enable Vss : Ground

PGM : Program

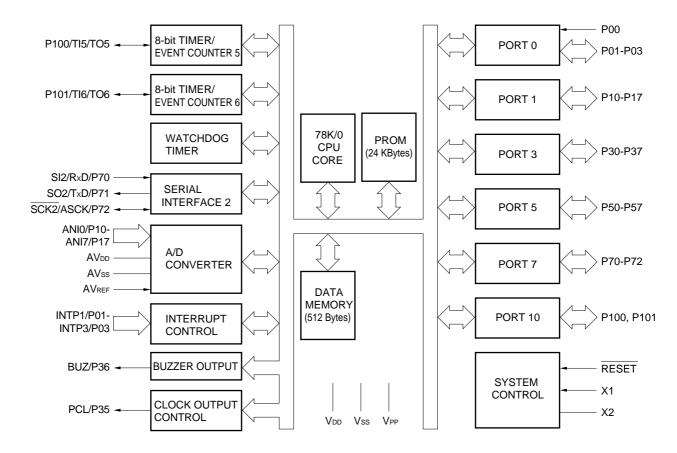

#### **BLOCK DIAGRAM**

## **CONTENTS**

| 1. | DIFFERENCES BETWEEN THE $\mu$ PD78P083(A) AND MASK ROM VERSIONS         | 13  |

|----|-------------------------------------------------------------------------|-----|

| 2. | PIN FUNCTIONS                                                           | 14  |

|    | 2.1 Pins in Normal Operating Mode                                       | 14  |

|    | 2.2 Pins in PROM Programming Mode                                       | 16  |

|    | 2.3 Pin Input/Output Circuits and Recommended Connection of Unused Pins | 16  |

| 3. | INTERNAL MEMORY SIZE SWITCHING REGISTER (IMS)                           | 18  |

| 4. | PROM PROGRAMMING                                                        | 19  |

|    | 4.1 Operating Modes                                                     |     |

|    | 4.2 PROM Write Procedure                                                |     |

|    | 4.3 PROM Read Procedure                                                 | 25  |

| 5. | ONE-TIME PROM VERSION SCREENING                                         | 26  |

| 6. | ELECTRICAL SPECIFICATIONS                                               | 27  |

| 7. | PACKAGE DRAWINGS                                                        | 45  |

| 8. | RECOMMENDED SOLDERING CONDITIONS                                        | 48  |

| ΑP | PENDIX A. DEVELOPMENT TOOLS                                             | 49  |

| ۸D | DENDIV D. DELATED DOCUMENTS                                             | E 1 |

## 1. DIFFERENCES BETWEEN THE $\mu$ PD78P083(A) AND MASK ROM VERSIONS

The  $\mu$ PD78P083(A) is a single-chip microcontroller with an on-chip one-time PROM.

Setting the memory size switching register (IMS) makes the functions except the PROM specification identical to the mask ROM versions.

Table 1-1 shows differences between the PROM version ( $\mu$ PD78P083(A)) and mask ROM versions ( $\mu$ PD78081(A) and  $\mu$ PD78082(A)).

Table 1-1. Differences between the  $\mu$ PD78P083(A) and Mask ROM Versions

| Parameter                            | μPD78P083(A)                          | Mask ROM Versions       |

|--------------------------------------|---------------------------------------|-------------------------|

| Internal ROM type                    | One-time PROM/EPROM                   | Mask ROM                |

| Internal ROM capacity                | 24 Kbytes                             | μPD78081(A) : 8 Kbytes  |

|                                      |                                       | μPD78082(A) : 16 Kbytes |

| Internal high-speed RAM capacity     | 512 bytes                             | μPD78081(A) : 256 bytes |

|                                      |                                       | μPD78082(A) : 384 bytes |

| Internal ROM and internal high-speed | Enable Note                           | Disable                 |

| RAM capacity change by               |                                       |                         |

| memory size switching register (IMS) |                                       |                         |

| IC pin                               | No                                    | Yes                     |

| V <sub>PP</sub> pin                  | Yes                                   | No                      |

| Electrical specifications            | Refer to a data sheet of each product |                         |

**Note** The internal PROM becomes 24 Kbytes and the internal high-speed RAM becomes 512 bytes by the RESET input.

## 2. PIN FUNCTIONS

## 2.1 Pins in Normal Operating Mode

## (1) Port pins

| Pin Name   | Input/Output | Function                   |                                 | After Reset | Alternate Function |

|------------|--------------|----------------------------|---------------------------------|-------------|--------------------|

| P00        | Input        | Port 0                     | Input only                      | Input       | _                  |

| P01        | Input/output | 4-bit input/output port    | Input/output is specifiable     | Input       | INTP1              |

| P02        |              |                            | bit-wise. When used as the      |             | INTP2              |

| P03        |              |                            | input port, it is possible to   |             | INTP3              |

|            |              |                            | connect a pull-up resistor by   |             |                    |

|            |              |                            | software.                       |             |                    |

| P10 to P17 | Input/output | Port 1                     |                                 | Input       | ANI0 to ANI7       |

|            |              | 8-bit input/output port    |                                 |             |                    |

|            |              | Input/output is specifiab  | le bit-wise.                    |             |                    |

| ļ          |              | When used as the input     | port, it is possible to connect |             |                    |

|            |              | a pull-up resistor by soft | ware. Note                      |             |                    |

| P30-P34    | Input/output | Port 3                     |                                 | Input       | _                  |

| P35        |              | 8-bit input/output port    |                                 |             | PCL                |

| P36        |              | Input/output is specifiab  | le bit-wise.                    |             | BUZ                |

| P37        |              | When used as the input     | port, it is possible to connect |             | _                  |

|            |              | a pull-up resistor by sof  | tware.                          |             |                    |

| P50 to P57 | Input/output | Port 5                     |                                 | Input       | _                  |

|            |              | 8-bit input/output port    |                                 |             |                    |

|            |              | Can drive up to seven L    | EDs directly.                   |             |                    |

|            |              | Input/output is specifiab  | le bit-wise.                    |             |                    |

|            |              | When used as the input     | port, it is possible to connect |             |                    |

|            |              | a pull-up resistor by sof  | tware.                          |             |                    |

| P70        | Input/output | Port 7                     |                                 | Input       | SI2/RxD            |

| P71        |              | 3-bit input/output port    |                                 |             | SO2/TxD            |

| P72        |              | Input/output is specifiab  | le bit-wise.                    |             | SCK2/ASCK          |

|            |              | When used as the input     |                                 |             |                    |

|            |              | a pull-up resistor by sof  |                                 |             |                    |

| P100       | Input/output | Port 10                    | Input                           | TI5/TO5     |                    |

| P101       |              | 2-bit input/output port    |                                 | TI6/TO6     |                    |

|            |              | Input/output is specifiab  |                                 |             |                    |

|            |              | When used as the input     |                                 |             |                    |

|            |              | a pull-up resistor by soft | tware.                          |             |                    |

**Note** When P10/ANI0-P17/ANI7 pins are used as the analog inputs for the A/D converter, set the port 1 to the input mode. The on-chip pull-up resistor is automatically disabled.

## (2) Non-port pins

| Pin Name         | Input/Output | Function                                                          | After Reset | Alternate Function |

|------------------|--------------|-------------------------------------------------------------------|-------------|--------------------|

| INTP1            | Input        | External interrupt input by which the active edge (rising edge,   | Input       | P01                |

| INTP2            |              | falling edge, or both rising and falling edges) can be specified. |             | P02                |

| INTP3            |              |                                                                   |             | P03                |

| SI2              | Input        | Serial interface serial data input.                               | Input       | P70/RxD            |

| SO2              | Output       | Serial interface serial data output.                              | Input       | P71/TxD            |

| SCK2             | Input/Output | Serial interface serial clock input/output.                       | Input       | P72/ASCK           |

| RxD              | Input        | Asynchronous serial interface serial data input.                  | Input       | P70/SI2            |

| TxD              | Output       | Asynchronous serial interface serial data output.                 | Input       | P71/SO2            |

| ASCK             | Input        | Asynchronous serial interface serial clock input.                 | Input       | P72/SCK2           |

| TI5              | Input        | External count clock input to 8-bit timer (TM5).                  | Input       | P100/TO5           |

| TI6              | -            | External count clock input to 8-bit timer (TM6).                  |             | P101/TO6           |

| TO5              | Output       | 8-bit timer output.                                               | Input       | P100/TI5           |

| TO6              |              |                                                                   |             | P101/TI6           |

| PCL              | Output       | Clock output. (for main system clock trimming)                    | Input       | P35                |

| BUZ              | Output       | Buzzer output.                                                    | Input       | P36                |

| ANI0 to ANI7     | Input        | A/D converter analog input.                                       | Input       | P10 to P17         |

| AVREF            | Input        | A/D converter reference voltage input.                            | _           | _                  |

| AV <sub>DD</sub> | -            | A/D converter analog power supply. Connected to VDD.              | -           | -                  |

| AVss             | -            | A/D converter ground potential. Connected to Vss.                 | -           | -                  |

| RESET            | Input        | System reset input.                                               | -           | -                  |

| X1               | Input        | Main system clock oscillation crystal connection.                 | _           | _                  |

| X2               | _            |                                                                   | _           | _                  |

| V <sub>DD</sub>  | _            | Positive power supply.                                            | _           | _                  |

| Vpp              | -            | High-voltage applied during program write/verification.           | _           | -                  |

|                  |              | Connected directly to Vss in normal operating mode.               |             |                    |

| Vss              | _            | Ground potential.                                                 | _           | _                  |

| NC               | _            | Does not internally connected. Connect to Vss.                    | _           | _                  |

|                  |              | (It can be left open)                                             |             |                    |

## 2.2 Pins in PROM Programming Mode

| Pin Name        | Input/Output | Function                                                                                  |

|-----------------|--------------|-------------------------------------------------------------------------------------------|

| RESET           | Input        | PROM programming mode setting                                                             |

|                 |              | When +5 V or +12.5 V is applied to the VPP pin and a low-level signal is applied to the   |

|                 |              | RESET pin, this chip is set in the PROM programming mode.                                 |

| VPP             | Input        | PROM programming mode setting and high-voltage applied during program write/verification. |

| A0 to A14       | Input        | Address bus                                                                               |

| D0-D7           | Input/output | Data bus                                                                                  |

| CE              | Input        | PROM enable input/program pulse input                                                     |

| ŌĒ              | Input        | Read strobe input to PROM                                                                 |

| PGM             | Input        | Program/program inhibit input in PROM programming mode.                                   |

| V <sub>DD</sub> | _            | Positive power supply                                                                     |

| Vss             | _            | Ground potential                                                                          |

## 2.3 Pin Input/Output Circuits and Recommended Connection of Unused Pins

Types of input/output circuits of the pins and recommeded connection of unused pins are shown in Table 2-1. For the configuration of each type of input/output circuit, see Figure 2-1.

Table 2-1. Type of Input/Output Circuit of Each Pin

| Pin Name             | Input/Output | Input/Output | Recommended Connection for Unused Pins       |

|----------------------|--------------|--------------|----------------------------------------------|

|                      | Circuit Type |              |                                              |

| P00                  | 2            | Input        | Connect to Vss.                              |

| P01/INTP1            | 8-A          | Input/Output | Independently connect to Vss via a resistor. |

| P02/INTP2            |              |              |                                              |

| P03/INTP3            |              |              |                                              |

| P10/ANI0 to P17/ANI7 | 11           | Input/Output | Independently connect to VDD or Vss via      |

| P30 to P32           | 5-A          |              | a resistor.                                  |

| P33, P34             | 8-A          |              |                                              |

| P35/PCL              | 5-A          |              |                                              |

| P36/BUZ              |              |              |                                              |

| P37                  |              |              |                                              |

| P50 to P57           | 5-A          |              |                                              |

| P70/SI2/RxD          | 8-A          |              |                                              |

| P71/SO2/TxD          | 5-A          |              |                                              |

| P72/SCK2/ASCK        | 8-A          |              |                                              |

| P100/TI5/TO5         | 8-A          |              |                                              |

| P101/TI6/TO6         |              |              |                                              |

| RESET                | 2            | Input        | _                                            |

| AVREF                | -            | _            | Connect to Vss.                              |

| AVDD                 |              |              | Connect to V <sub>DD</sub> .                 |

| AVss                 |              |              | Connect to Vss.                              |

| VPP                  |              |              | Connect directly to Vss.                     |

| NC                   |              |              | Connect to Vss (can leave open)              |

Type 2 Type 8-A pull-up ► P-ch enable IN C  $V_{DD}$ data · IN/OUT output disable Schmitt-triggered input with hysteresis characteristics V<sub>DD</sub> Type 5-A Type 11 pull-up enable pull-up enable  $V_{DD}$ data P-ch ⊸IN/OUT data output disable -N-ch O IN/OUT output Comparator disable V<sub>REF</sub> (threshold voltage) input input enable enable

Figure 2-1. Types of Pin Input/Output Circuits

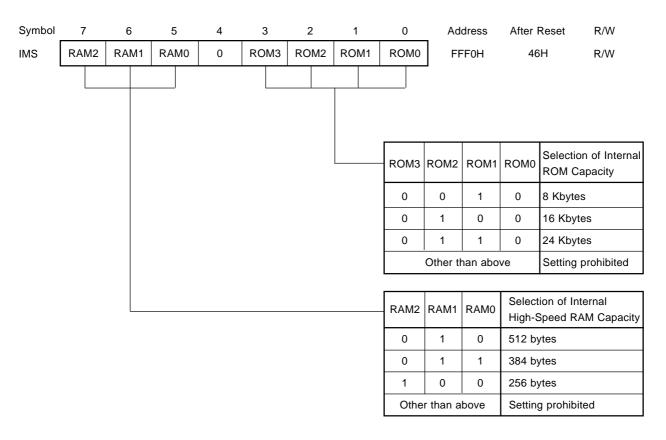

## 3. INTERNAL MEMORY SIZE SWITCHING REGISTER (IMS)

This is a register to disable use of part of internal memories by software. By setting this memory size switching register (IMS), it is possible to get the same memory mapping as that of the mask ROM versions with a different internal memory (ROM, RAM).

IMS is set with an 8-bit memory manipulation instruction.

RESET input sets IMS to 46H.

Figure 3-1. Internal Memory Size Switching Register Format

Table 3-1 shows the setting values of IMS which make the memory mapping the same as that of the mask ROM version.

Table 3-1. Internal Memory Size Switching Register Setting Values

| Target Mask ROM Versions | IMS Setting Value |

|--------------------------|-------------------|

| μPD78081(A)              | 82H               |

| μPD78082(A)              | 64H               |

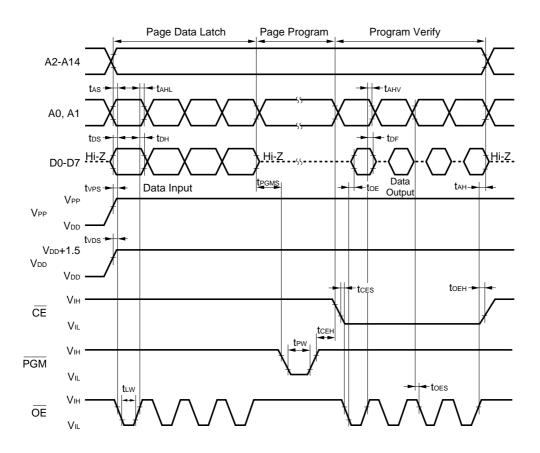

#### 4. PROM PROGRAMMING

The μPD78P083(A) has an internal 24-Kbyte PROM as a program memory. For programming, set the PROM programming mode with the V<sub>PP</sub> and RESET pins. For the connection of unused pins, refer to "PIN CONFIGURATIONS (TOP VIEW) (2) PROM programming mode."

Caution Programs must be written in addresses 0000H to 5FFFH (The last address 5FFFH must be specified). They cannot be written by a PROM programmer which cannot specify the write address.

## 4.1 Operating Modes

When +5 V or +12.5 V is applied to the  $\overline{\text{RESET}}$  pin, the PROM programming mode is set. This mode will become the operating mode as shown in Table 4-1 when the  $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{PGM}}$  pins are set as shown.

Further, when the read mode is set, it is possible to read the contents of the PROM.

Table 4-1. Operating Modes of PROM Programming

| Pin             | RESET | VPP     | V <sub>DD</sub> | CE | ŌĒ | PGM | D0 to D7       |

|-----------------|-------|---------|-----------------|----|----|-----|----------------|

| Operating Mode  |       |         |                 |    |    |     |                |

| Page data latch | L     | +12.5 V | +6.5 V          | Н  | L  | Н   | Data input     |

| Page write      |       |         |                 | Н  | Н  | L   | High-impedance |

| Byte write      |       |         |                 | L  | Н  | L   | Data input     |

| Program verify  |       |         |                 | L  | L  | Н   | Data output    |

| Program inhibit |       |         |                 | х  | Н  | Н   | High-impedance |

|                 |       |         |                 | х  | L  | L   |                |

| Read            |       | +5 V    | +5 V            | L  | L  | Н   | Data output    |

| Output disable  | 1     |         |                 | L  | Н  | х   | High-impedance |

| Standby         |       |         |                 | Н  | х  | х   | High-impedance |

x:LorH

#### (1) Read mode

Read mode is set if  $\overline{CE} = L$ ,  $\overline{OE} = L$  is set.

#### (2) Output disable mode

Data output becomes high-impedance, and is in the output disable mode, if  $\overline{OE} = H$  is set.

Therefore, it allows data to be read from any device by controlling the  $\overline{OE}$  pin, if multiple  $\mu$ PD78P083(A)s are connected to the data bus.

## (3) Standby mode

Standby mode is set if  $\overline{CE} = H$  is set.

In this mode, data outputs become high-impedance irrespective of the  $\overline{\text{OE}}$  status.

#### (4) Page data latch mode

Page data latch mode is set if  $\overline{CE} = H$ ,  $\overline{PGM} = H$ ,  $\overline{OE} = L$  are set at the beginning of page write mode. In this mode, 1 page 4-byte data is latched in an internal address/data latch circuit.

#### (5) Page write mode

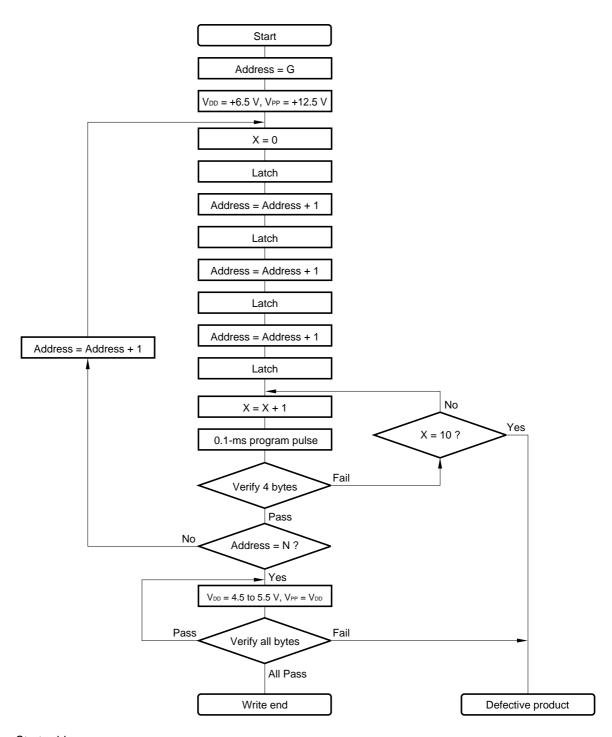

After 1 page 4 bytes of addresses and data are latched in the page data latch mode, a page write is executed by applying a 0.1-ms program pulse (active low) to the  $\overline{PGM}$  pin with  $\overline{CE} = H$ ,  $\overline{OE} = H$ . Then, program verification can be performed, if  $\overline{CE} = L$ ,  $\overline{OE} = L$  are set.

If programming is not performed by a one-time program pulse, X times (X - 10) write and verification operations should be executed repeatedly.

#### (6) Byte write mode

Byte write is executed when a 0.1-ms program pulse (active low) is applied to the  $\overline{PGM}$  pin with  $\overline{CE} = L$ ,  $\overline{OE} = H$ . Then, program verification can be performed if OE = L is set.

If programming is not performed by a one-time program pulse, X times (X - 10) write and verification operations should be executed repeatedly.

#### (7) Program verify mode

Program verify mode is set if  $\overline{CE} = L$ ,  $\overline{PGM} = H$ ,  $\overline{OE} = L$  are set.

In this mode, check if a write operation is performed correctly after the write.

#### (8) Program inhibit mode

Program inhibit mode is used when the  $\overline{\text{OE}}$  pin, VPP pin, and D0-D7 pins of multiple  $\mu$ PD78P083(A)s are connected in parallel and a write is performed to one of those devices.

When a write operation is performed, the page write mode or byte write mode described above is used. At this time, a write is not performed to a device which has the  $\overline{PGM}$  pin driven high.

#### 4.2 PROM Write Procedure

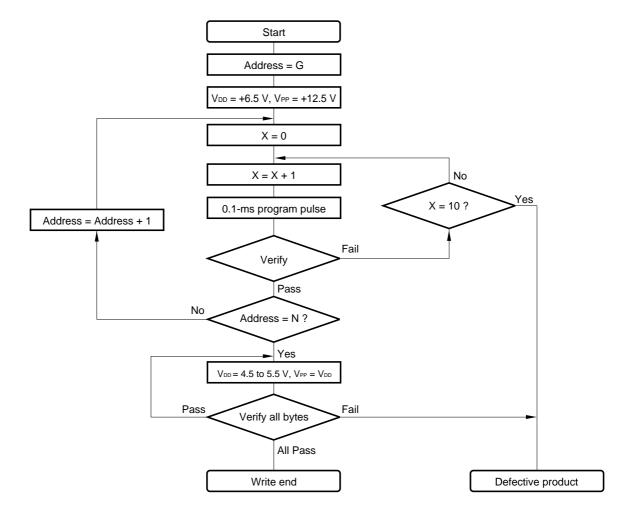

Figure 4-1. Page Program Mode Flow Chart

G = Start address

N = Program last address

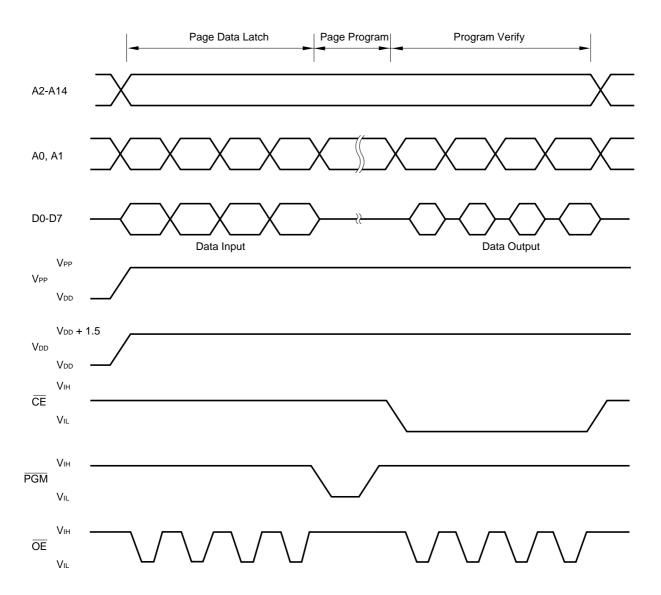

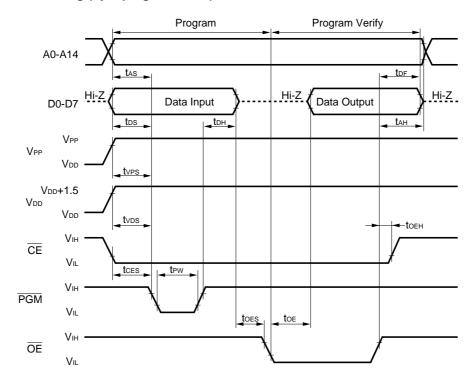

Figure 4-2. Page Program Mode Timing

Figure 4-3. Byte Program Mode Flow Chart

G = Start address

N = Program last address

Program Program Verify A0-A14 D0-D7 Data Input Data Output  $V_{PP}$  $V_{\text{DD}}$  $V_{DD} + 1.5$  $V_{DD}$  $V_{\text{DD}}$  $V_{\text{IH}}$ CE  $V_{\mathsf{IL}}$  $V_{\text{IH}}$ PGM  $V_{\mathsf{IL}}$ ŌĒ  $V_{\text{IL}}$

Figure 4-4. Byte Program Mode Timing

Cautions 1.  $\ensuremath{\text{V}_{\text{DD}}}$  should be applied before  $\ensuremath{\text{V}_{\text{PP}}}$  and removed after  $\ensuremath{\text{V}_{\text{PP}}}$ .

- 2. VPP must not exceed +13.5 V including overshoot.

- 3. Reliability may be adversely affected if removal/reinsertion is performed while +12.5 V is being applied to VPP.

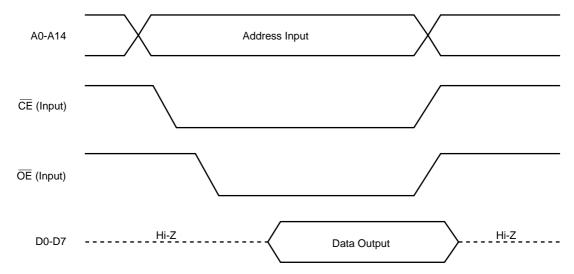

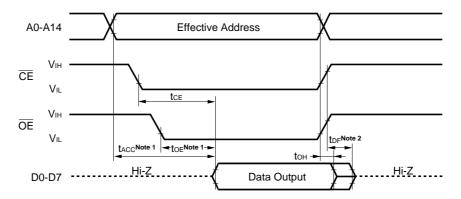

#### 4.3 PROM Read Procedure

The contents of PROM are readable to the external data bus (D0-D7) according to the read procedure shown below.

- (1) Fix the RESET pin at low level, supply +5 V to the VPP pin, and connect all other unused pins as shown in "PIN CONFIGURATIONS (TOP VIEW) (2) PROM programming mode".

- (2) Supply +5 V to the VDD and VPP pins.

- (3) Input address of read data into the A0 to A14 pins.

- (4) Read mode

- (5) Output data to D0 to D7 pins.

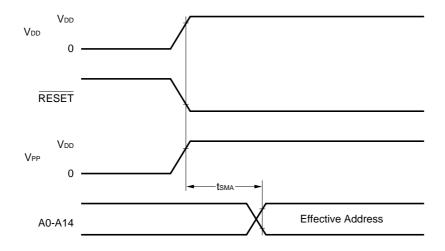

The timings of the above steps (2) to (5) are shown in Figure 4-5.

Figure 4-5. PROM Read Timings

## 5. ONE-TIME PROM VERSION SCREENING

The one-time PROM version ( $\mu$ PD78P083CU(A), 78P083GB(A)-3B4, 78P083GB(A)-3BS-MTX<sup>Note</sup>) cannot be tested completely by NEC before it is shipped, because of its structure. It is recommended to perform screening to verify PROM after writing necessary data and performing high-temperature storage under the condition below.

Note Under planning

| Storage Temperature | Storage Time |  |  |  |

|---------------------|--------------|--|--|--|

| 125°C               | 24 hours     |  |  |  |

NEC offers for an additional fee one-time PROM writing to marking, screening, and verify for products designated as QTOP Microcontroller. A fee-charged service for the  $\mu$ PD78P083(A) is under planning. Consult an NEC sales representative for details.

## 6. ELECTRICAL SPECIFICATIONS

**Absolute Maximum Ratings** (TA = 25°C)

| Parameter                     | Symbol           | Test Conditi                      | ons                   |                               | Ratings                       | Unit |

|-------------------------------|------------------|-----------------------------------|-----------------------|-------------------------------|-------------------------------|------|

| Supply voltage                | V <sub>DD</sub>  |                                   |                       |                               | -0.3 to +7.0                  | V    |

|                               | V <sub>PP</sub>  |                                   |                       |                               | -0.3 to +13.5                 | V    |

|                               | AVDD             |                                   |                       |                               | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                               | AVREF            |                                   |                       |                               | -0.3 to V <sub>DD</sub> + 0.3 | V    |

|                               | AVss             |                                   |                       |                               | -0.3 to +0.3                  | V    |

| Input voltage                 | VI1              |                                   |                       | -0.3 to V <sub>DD</sub> + 0.3 |                               |      |

|                               | V <sub>I2</sub>  | A9                                | PROM programming mode |                               | -0.3 to +13.5                 | V    |

| Output voltage                | Vo               |                                   |                       |                               | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Analog input voltage          | Van              | P10 to P17                        | Analog input          | pins                          | AVss - 0.3 to AVREF + 0.3     | V    |

| Output current, high          | Іон              | Per pin                           | •                     |                               | -10                           | mA   |

|                               |                  | Total for P1                      | 0 to P17, P50         | to P54,                       | -15                           | mA   |

|                               |                  | P70 to P72, P100, P101            |                       |                               |                               |      |

|                               |                  | Total for P01 to P03, P30 to P37, |                       |                               | -15                           | mA   |

|                               |                  | P55 to P57                        |                       |                               |                               |      |

| Output current, low           | IOL Note         | Note Per pin                      |                       | Peak value                    | 30                            | mA   |

|                               |                  |                                   |                       | r.m.s. value                  | 15                            | mA   |

|                               |                  | Total for P5                      | 0 to P54              | Peak value                    | 100                           | mA   |

|                               |                  |                                   |                       | r.m.s. value                  | 70                            | mA   |

|                               |                  | Total for P5                      | 5 to P57              | Peak value                    | 100                           | mA   |

|                               |                  |                                   |                       | r.m.s. value                  | 70                            | mA   |

|                               |                  | Total for P1                      | 0 to P17,             | Peak value                    | 50                            | mA   |

|                               |                  | P70 to P72,                       | P100, P101            | r.m.s. value                  | 20                            | mA   |

|                               |                  | Total for P0                      | 1 to P03,             | Peak value                    | 50                            | mA   |

|                               |                  | P30 to P37                        |                       | r.m.s. value                  | 20                            | mA   |

| Operating ambient temperature | TA               |                                   |                       |                               | -40 to +85                    | °C   |

| Storage temperature           | T <sub>stg</sub> |                                   |                       |                               | -65 to +150                   | °C   |

**Note** The r.m.s. value should be calculated as follows: [r.m.s. value] = [Peak value]  $\times \sqrt{\text{Duty}}$

Caution If the absolute maximum rating of even one of the above parameters is exceeded, the quality of the product may be degraded. The absolute maximum ratings are therefore the rated values that may, if exceeded, physically damage the product. Be sure to use the product with all the absolute maximum ratings observed.

Remark Unless otherwise specified, dual-function pin characteristics are the same as port pin characteristics.

Capacitance (TA = 25°C, VDD = VSS = 0 V)

| Parameter         | Symbol | Test Conditions                             |                         |  | TYP. | MAX. | Unit |

|-------------------|--------|---------------------------------------------|-------------------------|--|------|------|------|

| Input capacitance | CIN    | f = 1 MHz, Unmeasured pins returned to 0 V. |                         |  |      | 15   | pF   |

| I/O capacitance   | Сю     | f = 1 MHz,                                  | P01 to P03, P10 to P17, |  |      | 15   | pF   |

|                   |        | Unmeasured pins                             | P30 to P37, P50 to P57, |  |      |      |      |

|                   |        | returned to 0 V.                            | P70 to P72, P100, P101  |  |      |      |      |

Remark Unless otherwise specified, dual-function pin characteristics are the same as port pin characteristics.

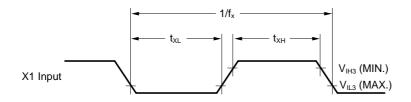

Main System Clock Oscillator Characteristics (TA = -40 to +85°C, VDD = 1.8 to 5.5 V)

| Resonator         | Recommended<br>Circuit | Parameter                                      | Test Conditions                                                 | MIN. | TYP. | MAX. | Unit |

|-------------------|------------------------|------------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| Ceramic resonator |                        | Oscillation frequency (fX) Note 1              | V <sub>DD</sub> = Oscillation voltage range                     | 1.0  |      | 5.0  | MHz  |

| C2= C             | C2± C1 ±               | Oscillation stabilization time Note 2          | After V <sub>DD</sub> came to MIN. of oscillation voltage range |      |      | 4    | ms   |

| Crystal resonator | Crystal VPP X2 X1      | Oscillation frequency (fX) Note 1              |                                                                 | 1.0  |      | 5.0  | MHz  |

|                   | C2+ C1 +               | Oscillation stabilization                      | V <sub>DD</sub> = 4.5 to 5.5 V                                  |      |      | 10   | ms   |

|                   | 1///                   | time Note 2                                    |                                                                 |      |      | 30   |      |

| External clock    | X2 X1                  | X1 input frequency  (fX) Note 1                |                                                                 | 1.0  |      | 5.0  | MHz  |

|                   | ™PD74HCU04 Å           | X1 input high- and low-level widths (txH, txL) |                                                                 | 85   |      | 500  | ns   |

- Notes 1. Only the oscillator characteristics are shown. For the instruction execution time, refer to AC Characteristics

- 2. Time required for oscillation to stabilize after a reset or the STOP mode has been released.

Caution When using the oscillation circuit of the main system clock, wire the portion enclosed in broken lines in the figures as follows to avoid adverse influences on the wiring capacitance:

- Keep the wiring length as short as possible.

- Do not cross the wiring over other signal lines.

- Do not route the wiring in the vicinity of lines through which a high fluctuating current flows.

- Always keep the ground point of the capacitor of the oscillation circuit at the same potential as Vss.

- Do not connect the power source pattern through which a high current flows.

- Do not extract signals from the oscillation circuit.

## **DC Characteristics** (TA = -40 to +85°C, VDD = 1.8 to 5.5 V)

| Parameter                 | Symbol           | Test C                                              | Conditions                                | MIN.                  | TYP. | MAX.                | Unit      |

|---------------------------|------------------|-----------------------------------------------------|-------------------------------------------|-----------------------|------|---------------------|-----------|

| Input voltage, high       | V <sub>IH1</sub> | P10 to P17, P30 to P32, P35 to P37, P50 to P57,     | V <sub>DD</sub> = 2.7 to 5.5 V            | 0.7V <sub>DD</sub>    |      | V <sub>DD</sub>     | V         |

|                           |                  | P71                                                 |                                           | 0.8V <sub>DD</sub>    |      | V <sub>DD</sub>     | V         |

|                           | V <sub>IH2</sub> | P00 to P03, P33, P34,                               | V <sub>DD</sub> = 2.7 to 5.5 V            | 0.8V <sub>DD</sub>    |      | V <sub>DD</sub>     | V         |

|                           |                  | P70, P72, P100,<br>P101, RESET                      |                                           | 0.85V <sub>DD</sub>   |      | V <sub>DD</sub>     | V         |

|                           | V <sub>IH3</sub> | X1, X2                                              | V <sub>DD</sub> = 2.7 to 5.5 V            | V <sub>DD</sub> - 0.5 |      | V <sub>DD</sub>     | V         |

|                           |                  |                                                     |                                           | V <sub>DD</sub> - 0.2 |      | V <sub>DD</sub>     | V         |

| Input voltage, low        | VIL1             | P10 to P17, P30 to P32, P35 to P37, P50 to P57,     | V <sub>DD</sub> = 2.7 to 5.5 V            | 0                     |      | 0.3V <sub>DD</sub>  | V         |

|                           |                  | P71                                                 |                                           | 0                     |      | 0.2V <sub>DD</sub>  | V         |

|                           | V <sub>IL2</sub> | P00 to P03, P33, P34, P70, P72, P100,               | V <sub>DD</sub> = 2.7 to 5.5 V            | 0                     |      | 0.2V <sub>DD</sub>  | V         |

|                           |                  | P101, RESET                                         |                                           | 0                     |      | 0.15V <sub>DD</sub> | V         |

|                           | VIL3             | X1, X2                                              | V <sub>DD</sub> = 2.7 to 5.5 V            | 0                     |      | 0.4                 | V         |

|                           |                  |                                                     |                                           | 0                     |      | 0.2                 | V         |

| Output voltage, high      | Vон              | V <sub>DD</sub> = 4.5 to 5.5 V, I <sub>OH</sub> = - | –1 mA                                     | V <sub>DD</sub> - 1.0 |      |                     | V         |

|                           |                  | Іон = −100 μА                                       |                                           | V <sub>DD</sub> - 0.5 |      |                     | V         |

| Output voltage, low       | Vol              | P50 to P57                                          | $V_{DD} = 2.0 \text{ to } 4.5 \text{ V},$ |                       |      | 0.8                 | V         |

|                           |                  |                                                     | IoL = 10 mA                               |                       |      |                     |           |

|                           |                  |                                                     | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V},$ |                       | 0.4  | 2.0                 | V         |

|                           |                  |                                                     | IoL = 15 mA                               |                       |      |                     |           |

|                           |                  | P01 to P03, P10 to P17,                             | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V},$ |                       |      | 0.4                 | V         |

|                           |                  | P30 to P37, P70 to P72,                             | IoL = 1.6 mA                              |                       |      |                     |           |

|                           |                  | P100, P101                                          | $IoL = 400 \mu A$                         |                       |      | 0.5                 | V         |

| Input-leak current, high  | ILIH1            | VIN = VDD                                           | P00 to P03, P10 to P17,                   |                       |      | 3                   | μΑ        |

|                           |                  |                                                     | P30 to P37, P50 to P57,                   |                       |      |                     |           |

|                           |                  |                                                     | P70 to P72, P100,                         |                       |      |                     |           |

|                           |                  |                                                     | P101, RESET                               |                       |      |                     |           |

|                           | ILIH2            |                                                     | X1, X2                                    |                       |      | 20                  | μΑ        |

| Input-leak current, low   | ILIL1            | Vin = 0 V                                           | P00 to P03, P10 to P17,                   |                       |      | -3                  | μΑ        |

|                           |                  |                                                     | P30 to P37, P50 to P57,                   |                       |      |                     |           |

|                           |                  |                                                     | P70 to P72, P100,                         |                       |      |                     |           |

|                           |                  |                                                     | P101, RESET                               |                       |      |                     |           |

|                           | ILIL2            |                                                     | X1, X2                                    |                       |      | -20                 | μΑ        |

| Output leak current, high | Ісон             | Vout = Vdd                                          |                                           |                       |      | 3                   | μΑ        |

| Output leak current, low  | ILOL             | Vout = 0 V                                          |                                           |                       |      | -3                  | μΑ        |

| Software pull-up resistor | R                | VIN = 0 V                                           | P01 to P03, P10 to P17,                   | 15                    | 40   | 90                  | $k\Omega$ |

|                           |                  |                                                     | P30 to P37, P50 to P57,                   |                       |      |                     |           |

|                           |                  |                                                     | P70 to P72, P100,                         |                       |      |                     |           |

|                           |                  |                                                     | P101                                      |                       |      |                     |           |

Remark Unless otherwise specified, dual-function pin characteristics are the same as port pin characteristics.

## **DC Characteristics** (TA = -40 to +85°C, VDD = 1.8 to 5.5 V)

| Parameter             | Symbol           | Test Co                                | nditions                                         | MIN. | TYP. | MAX. | Unit |

|-----------------------|------------------|----------------------------------------|--------------------------------------------------|------|------|------|------|

| Supply current Note 1 | I <sub>DD1</sub> | 5.0-MHz crystal                        | $V_{DD} = 5.0 \text{ V} \pm 10\% \text{ Note 4}$ |      | 5.4  | 16.2 | mA   |

|                       |                  | oscillation operating                  | $V_{DD} = 3.0 \text{ V} \pm 10\% \text{ Note 5}$ |      | 0.8  | 2.4  | mA   |

|                       |                  | mode (fxx = $2.5 \text{ MHz}$ ) Note 2 | $V_{DD} = 2.0 \text{ V} \pm 10\% \text{ Note 5}$ |      | 0.45 | 1.35 | mA   |

|                       |                  | 5.0-MHz crystal oscillation            | $V_{DD} = 5.0 \text{ V} \pm 10\% \text{ Note 4}$ |      | 9.5  | 28.5 | mA   |

|                       |                  | operating mode                         | $V_{DD} = 3.0 \text{ V} \pm 10\% \text{ Note 5}$ |      | 1.0  | 3.0  | mA   |

|                       |                  | (fxx = 5.0 MHz) Note 3                 |                                                  |      |      |      |      |

|                       | I <sub>DD2</sub> | 5.0-MHz crystal oscillation            | V <sub>DD</sub> = 5.0 V ± 10%                    |      | 1.4  | 4.2  | mA   |

|                       |                  | HALT mode                              | V <sub>DD</sub> = 3.0 V ± 10%                    |      | 0.5  | 1.5  | mA   |

|                       |                  | (fxx = 2.5 MHz) Note 2                 | $V_{DD} = 2.0 \text{ V} \pm 10\%$                |      | 280  | 840  | μΑ   |

|                       |                  | 5.0-MHz crystal oscillation            | V <sub>DD</sub> = 5.0 V ± 10%                    |      | 1.6  | 4.8  | mA   |

|                       |                  | HALT mode                              | V <sub>DD</sub> = 3.0 V ± 10%                    |      | 0.65 | 1.95 | mA   |

|                       |                  | (fxx = 5.0 MHz) Note 3                 |                                                  |      |      |      |      |

|                       | IDD3             | STOP mode                              | V <sub>DD</sub> = 5.0 V ± 10%                    |      | 0.1  | 30   | μΑ   |

|                       |                  |                                        | V <sub>DD</sub> = 3.0 V ± 10%                    |      | 0.05 | 10   | μΑ   |

|                       |                  |                                        | V <sub>DD</sub> = 2.0 V ± 10%                    |      | 0.05 | 10   | μΑ   |

**Notes** 1. Not including AVREF, AVDD currents or port currents (including current flowing into internal pull-up resistors).

**2.** fxx = fx/2 operation (when oscillation mode selection register (OSMS) is set to 00H).

**3.** fxx = fx operation (when oscillation mode selection register (OSMS) is set to 01H).

4. High-speed mode operation (when processor clock control register (PCC) is set to 00H).

**5.** Low-speed mode operation (when processor clock control register (PCC) is set to 04H).

Remark fxx: Main system clock frequency (fx or fx/2) fx: Main system clock oscillation frequency

#### **AC Characteristics**

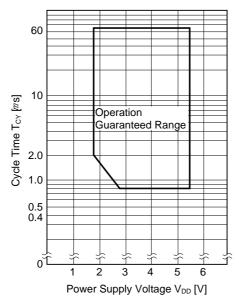

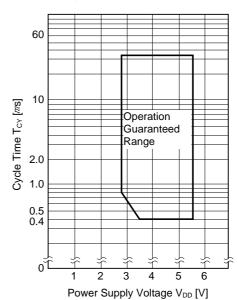

(1) Basic Operation (TA =  $-40 \text{ to } +85^{\circ}\text{C}$ , VDD = 1.8 to 5.5 V)

| Parameter              | Symbol        | Test                           | Conditions                               | MIN. | TYP. | MAX. | Unit |

|------------------------|---------------|--------------------------------|------------------------------------------|------|------|------|------|

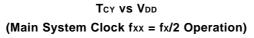

| Cycle time             | Tcy           | fxx = fx/2 Note1               | $V_{DD} = 2.7 \text{ to } 5.5 \text{ V}$ | 0.8  |      | 64   | μs   |

| (minimum instruction   |               |                                |                                          | 2.0  |      | 64   | μs   |

| execution time)        |               | fxx = fx/ Note2                | 3.5 V - VDD - 5.5 V                      | 0.4  |      | 32   | μs   |

|                        |               |                                | 2.7 V - VDD < 3.5 V                      | 0.8  |      | 32   | μs   |

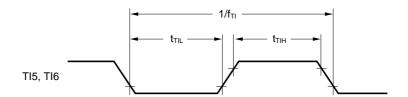

| TI5, TI6               | f⊤ı           | V <sub>DD</sub> = 4.5 to 5.5 V |                                          | 0    |      | 4    | MHz  |

| input frequency        |               |                                |                                          | 0    |      | 275  | kHz  |

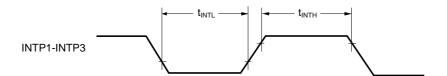

| TI5, TI6 input high-/  | <b>t</b> тін, | V <sub>DD</sub> = 4.5 to 5.5 V |                                          | 100  |      |      | ns   |

| low-level widths       | t⊤ı∟          |                                |                                          | 1.8  |      |      | μs   |

| Interrupt input high-/ | tinth,        | V <sub>DD</sub> = 2.7 to 5.5 V |                                          | 10   |      |      | μs   |

| low-level widths       | tintl         |                                |                                          | 20   |      |      | μs   |

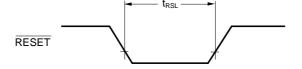

| RESET low-level width  | trsL          | V <sub>DD</sub> = 2.7 to 5.5 V |                                          | 10   |      |      | μs   |

|                        |               |                                |                                          | 20   |      |      | μs   |

Notes 1. When oscillation mode selection register (OSMS) is set to 00H.

2. When OSMS is set to 01H.

Remark fxx: Main system clock frequency (fx or fx/2) fx: Main system clock oscillation frequency

$T_{CY} vs V_{DD}$ (Main System Clock fxx = fx Operation)

## (2) Serial Interface ( $T_A = -40 \text{ to } +85^{\circ}\text{C}$ , $V_{DD} = 1.8 \text{ to } 5.5 \text{ V}$ )

## (a) 3-wired serial I/O mode (SCK2 ··· internal clock output)

| Parameter                         | Symbol            | Test Conditions                 | MIN.        | TYP. | MAX. | Unit |

|-----------------------------------|-------------------|---------------------------------|-------------|------|------|------|

| SCK2 cycle time                   | tkcy1             | 4.5 V - VDD - 5.5 V             | 800         |      |      | ns   |

|                                   |                   | 2.7 V - VDD < 4.5 V             | 1600        |      |      | ns   |

|                                   |                   | 2.0 V - VDD < 2.7 V             | 3200        |      |      | ns   |

|                                   |                   |                                 | 4800        |      |      | ns   |

| SCK2 high-/low-level width        | <b>t</b> кн1,     | V <sub>DD</sub> = 4.5 to 5.5 V  | tkcy1/2-50  |      |      | ns   |

|                                   | t <sub>KL1</sub>  |                                 | tксү1/2-100 |      |      | ns   |

| SI2 setup time (to SCK2 ↑)        | tsıĸ1             | 4.5 V - VDD - 5.5 V             | 100         |      |      | ns   |

|                                   |                   | 2.7 V - VDD < 4.5 V             | 150         |      |      | ns   |

|                                   |                   | 2.0 V - V <sub>DD</sub> < 2.7 V | 300         |      |      | ns   |

|                                   |                   |                                 | 400         |      |      | ns   |

| SI2 hold time (from SCK2 1)       | t <sub>KSI1</sub> |                                 | 400         |      |      | ns   |

| SCK2 ↓ → SO2<br>output delay time | tkso1             | C = 100 pF <sup>Note</sup>      |             |      | 300  | ns   |

Note C is the SCK2, SO2 output line load capacitance.

## (b) 3-wired serial I/O mode (SCK2 ··· external clock input)

| Parameter                                                  | Symbol            | Test C                         | onditions                       | MIN. | TYP. | MAX. | Unit |

|------------------------------------------------------------|-------------------|--------------------------------|---------------------------------|------|------|------|------|

| SCK2 cycle time                                            | tkCY2             | 4.5 V - VDD - 5.5 V            |                                 | 800  |      |      | ns   |

|                                                            |                   | 2.7 V - VDD < 4.5 V            |                                 | 1600 |      |      | ns   |

|                                                            |                   | 2.0 V - VDD < 2.7 V            |                                 | 3200 |      |      | ns   |

|                                                            |                   |                                |                                 | 4800 |      |      | ns   |

| SCK2 high-/low-level width                                 | <b>t</b> кн2,     | 4.5 V - VDD - 5.5 V            | 4.5 V - V <sub>DD</sub> - 5.5 V |      |      |      | ns   |

|                                                            | t <sub>KL2</sub>  | 2.7 V - VDD < 4.5 V            | 2.7 V - V <sub>DD</sub> < 4.5 V |      |      |      | ns   |

|                                                            |                   | 2.0 V - VDD < 2.7 V            |                                 | 1600 |      |      | ns   |

|                                                            |                   |                                |                                 | 2400 |      |      | ns   |

| SI2 setup time (to SCK2 ↑)                                 | tsık2             | V <sub>DD</sub> = 2.0 to 5.5 V |                                 | 100  |      |      | ns   |

|                                                            |                   |                                |                                 | 150  |      |      | ns   |

| SI2 hold time (from SCK2 ↑)                                | t <sub>KSI2</sub> |                                |                                 | 400  |      |      | ns   |

| $\overline{\text{SCK2}} \downarrow \rightarrow \text{SO2}$ | <b>t</b> KSO2     | C = 100 pF <sup>Note</sup>     | V <sub>DD</sub> = 2.0 to 5.5 V  |      |      | 300  | ns   |

| output delay time                                          |                   |                                |                                 |      |      | 500  | ns   |

| SCK2 rise, fall time                                       | t <sub>R2</sub> , |                                |                                 |      |      | 1000 | ns   |

|                                                            | <b>t</b> F2       |                                |                                 |      |      |      |      |

Note C is the SO2 output line load capacitance.

## (c) UART mode (Dedicated baud rate generator output)

| Parameter     | Symbol | Test Conditions                 | MIN. | TYP. | MAX.  | Unit |

|---------------|--------|---------------------------------|------|------|-------|------|

| Transfer rate |        | 4.5 V - V <sub>DD</sub> - 5.5 V |      |      | 78125 | bps  |

|               |        | 2.7 V - VDD < 4.5 V             |      |      | 39063 | bps  |

|               |        | 2.0 V - VDD < 2.7 V             |      |      | 19531 | bps  |

|               |        |                                 |      |      | 9766  | bps  |

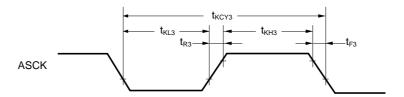

## (d) UART mode (External clock input)

| Parameter                  | Symbol            | Test Conditions                 | MIN. | TYP. | MAX.  | Unit |

|----------------------------|-------------------|---------------------------------|------|------|-------|------|

| ASCK cycle time            | tксүз             | 4.5 V - VDD - 5.5 V             | 800  |      |       | ns   |

|                            |                   | 2.7 V - VDD < 4.5 V             | 1600 |      |       | ns   |

|                            |                   | 2.0 V - V <sub>DD</sub> < 2.7 V | 3200 |      |       | ns   |

|                            |                   |                                 | 4800 |      |       | ns   |

| ASCK high-/low-level width | <b>t</b> кнз,     | 4.5 V - VDD - 5.5 V             | 400  |      |       | ns   |

|                            | <b>t</b> кL3      | 2.7 V - V <sub>DD</sub> < 4.5 V | 800  |      |       | ns   |

|                            |                   | 2.0 V - VDD < 2.7 V             | 1600 |      |       | ns   |

|                            |                   |                                 | 2400 |      |       | ns   |

| Transfer rate              |                   | 4.5 V - VDD - 5.5 V             |      |      | 39063 | bps  |

|                            |                   | 2.7 V - VDD < 4.5 V             |      |      | 19531 | bps  |

|                            |                   | 2.0 V - VDD < 2.7 V             |      |      | 9766  | bps  |

|                            |                   |                                 |      |      | 6510  | bps  |

| ASCK rise, fall time       | t <sub>R3</sub> , |                                 |      |      | 1000  | ns   |

|                            | <b>t</b> F3       |                                 |      |      |       |      |

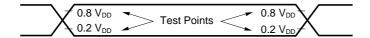

## AC Timing Test Point (Excluding X1 Input)

## **Clock Timing**

## **TI Timing**

## **Serial Transfer Timing**

## 3-wired serial I/O mode:

## **UART** mode (external clock input):

## A/D Converter Characteristics (TA = -40 to +85°C, AVDD = VDD = 2.7 to 5.5 V, AVSS = VSS = 0 V)

| Parameter             | Symbol        | Test Conditions      | MIN.   | TYP. | MAX.  | Unit     |

|-----------------------|---------------|----------------------|--------|------|-------|----------|

| Resolution            |               |                      | 8      | 8    | 8     | bit      |

| Total error Note      |               | 2.7 V - AVREF - AVDD |        |      | 1.4   | %        |

| Conversion time       | tconv         |                      | 19.1   |      | 200   | μs       |

| Sampling time         | <b>t</b> SAMP |                      | 12/fxx |      |       | μs       |

| Analog input voltage  | VIAN          |                      | AVss   |      | AVREF | <b>V</b> |

| Reference voltage     | AVREF         |                      | 2.7    |      | AVDD  | V        |

| AVREF-AVss resistance | Rairef        |                      | 4      | 14   |       | kΩ       |

Note Excluding quantization error (±1/2 LSB). Shown as a percentage of the full scale value.

**Remark** fxx: Main system clock frequency (fx or fx/2) fx: Main system clock oscillation frequency

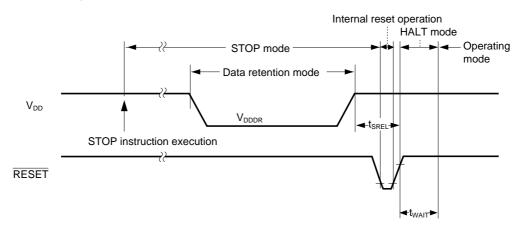

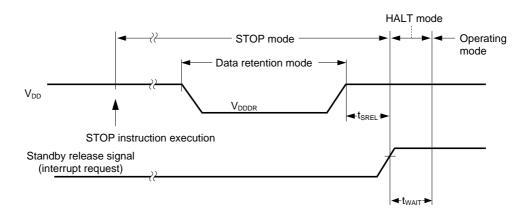

## Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics (TA = -40 to +85°C)

| Parameter                      | Symbol | Test Conditions      | MIN. | TYP.   | MAX. | Unit |

|--------------------------------|--------|----------------------|------|--------|------|------|

| Data retention supply voltage  | VDDDR  |                      | 1.8  |        | 5.5  | V    |

| Data retention supply current  | Idddr  | VDDDR = 1.8 V        |      | 0.1    | 10   | μΑ   |

| Release signal set time        | tsrel  |                      | 0    |        |      | μs   |

| Oscillation stabilization wait | twait  | Release by RESET     |      | 217/fx |      | ms   |

| time                           |        | Release by interrupt |      | Note   |      | ms   |

**Note** 2<sup>12</sup>/fxx or 2<sup>14</sup>/fxx to 2<sup>17</sup>/fxx can be selected by bit 0 to bit 2 (OSTS0 to OSTS2) of oscillation stabilization time selection register (OSTS).

Remark fxx: Main system clock frequency (fx or fx/2) fx: Main system clock oscillation frequency

## Data Retention Timing (STOP mode released by RESET)

## Data Retention Timing (Standby release signal: STOP mode released by interrupt request signal)

## Interrupt Input Timing

## **RESET** Input Timing

## **PROM Programming Characteristics**

## **DC Characteristics**

## (1) **PROM Write Mode** (TA = $25 \pm 5\frac{1}{2}$ C, VDD = $6.5 \pm 0.25$ V, VPP = $12.5 \pm 0.3$ V)

| Parameter                      | Symbol          | Symbol <sup>Note</sup> | Test Conditions | MIN.                  | TYP. | MAX.               | Unit |

|--------------------------------|-----------------|------------------------|-----------------|-----------------------|------|--------------------|------|

| Input voltage, high            | ViH             | VIH                    |                 | 0.7V <sub>DD</sub>    |      | V <sub>DD</sub>    | V    |

| Input voltage, low             | VIL             | VIL                    |                 | 0                     |      | 0.3V <sub>DD</sub> | V    |

| Output voltage, high           | Vон             | Vон                    | Iон = −1 mA     | V <sub>DD</sub> - 1.0 |      |                    | V    |

| Output voltage, low            | Vol             | Vol                    | IoL = 1.6 mA    |                       |      | 0.4                | V    |

| Input leakage current          | lu              | Li                     | 0 - VIN - VDD   | -10                   |      | +10                | μΑ   |

| V <sub>PP</sub> supply voltage | V <sub>PP</sub> | V <sub>PP</sub>        |                 | 12.2                  | 12.5 | 12.8               | ٧    |