August 1998

File Number

3207.2

# Power Control IC Single Chip Power Supply

The HIP5060 is a complete power control IC, incorporating both the high power DMOS transistor, CMOS logic and low level analog circuitry on the same Intelligent Power IC. Both the standard "Boost" and the "SEPIC" (Single-Ended Primary Inductance Converter) power supply topologies are easily implemented with this single control IC.

Special power transistor current sensing circuitry is incorporated that minimizes losses due to the monitoring circuitry. Moreover, over-temperature and over-voltage detection circuitry is incorporated within the IC to monitor the chip temperature and the actual power supply output voltage. These circuits can disable the drive to the power transistor to protect both the transistor and, most importantly, the load from over-voltage.

As a result of the power DMOS transistor's current and voltage capability (10A and 60V), power supplies with output power capability up to 100 watts are possible.

#### **Features**

- · Single Chip Current Mode Control IC

- 60V, 10A On-Chip DMOS Transistor

- Thermal Protection

- Over-Voltage Protection

- Over-Current Protection

- 1MHz Operation or External Clock

- Synchronization Output

- On-Chip Reference Voltage 5.1V

- Output Rise and Fall Times ~ 3ns

- Designed for 27V to 45V Operation

# **Applications**

- · Single Chip Power Supplies

- Current Mode PWM Applications

- Distributed Power Supplies

- Multiple Output Converters

### Ordering Information

| PART NUMBER | TEMPERATURE<br>RANGE | PACKAGE     |

|-------------|----------------------|-------------|

| HIP5060DY   | 0°C to +85°C         | 37 Pad Chip |

| HIP5060DW   | 0°C to +85°C         | Wafer       |

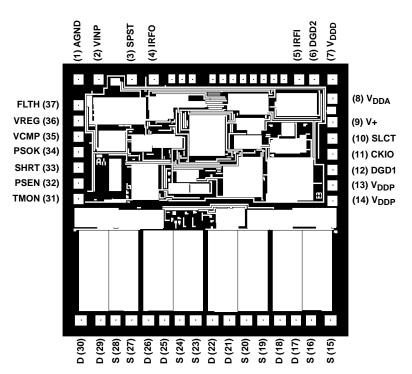

## Chip

NOTE: Unused pads are for trim and test. 153 mils x 165 mils (3.88mm x 4.19mm)

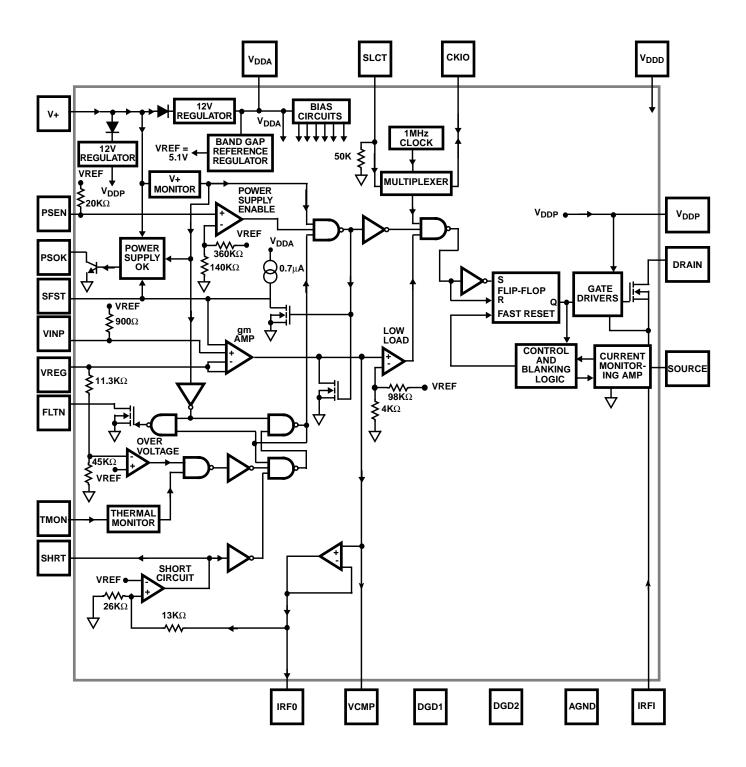

# Simplified Block Diagram

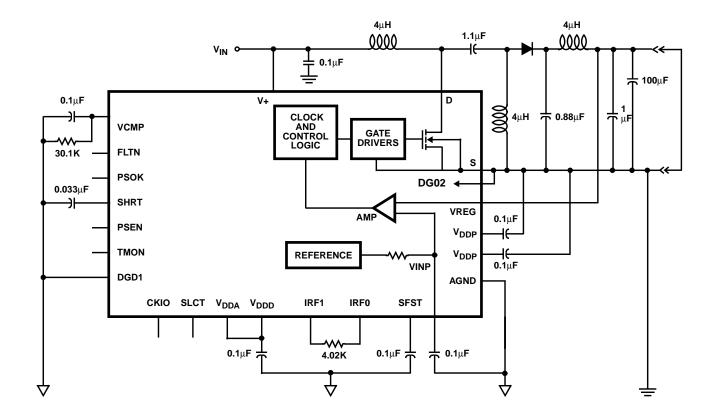

**TYPICAL SEPIC CONFIGURATION**

#### HIP5060

## **Absolute Maximum Ratings**

#### **Thermal Information**

| DC Supply Voltage, V+0.3V to 45V                   | Thermal Resist |

|----------------------------------------------------|----------------|

| DMOS Drain Voltage0.3V to 60V                      | (Solder Mour   |

| DMOS Drain Current                                 | 0.050" Thick   |

| DC Logic Supply0.3V to 16V                         | Maximum Junc   |

| Output Voltage, Logic Outputs0.3V to 16V           | (Controlled B  |

| Input Voltage, Analog and Logic0.3V to 16V         |                |

| Operating Junction Temperature Range 0°C to +110°C |                |

| Storage Temperature Range55°C to +150°C            |                |

stance  $\theta_{\text{JC}}$ ınted to ..... 3°C/W Max Copper Heat Sink) By Thermal Shutdown Circuit)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### Electrical Specifications V+ = 36V, T<sub>J</sub> = 0°C to +110°C; Unless Otherwise Specified

| SYMBOL                 | PARAMETER                                                          | TEST CONDITIONS                                   | MIN  | TYP  | MAX   | UNITS             |

|------------------------|--------------------------------------------------------------------|---------------------------------------------------|------|------|-------|-------------------|

| DEVICE PARA            | METERS                                                             | •                                                 |      |      |       |                   |

| l+                     | Supply Current                                                     | PSEN = 12V                                        | -    | 19.5 | 32    | mA                |

| $V_{DDA}$              | Internal Regulator Output<br>Voltage                               | V+ = 15V to 45V, I <sub>OUT</sub> = 10mA          | 11.0 | -    | 13.2  | V                 |

| VINP                   | Reference Voltage                                                  | I <sub>VINP</sub> = 0mA                           | 5.01 | 5.1  | 5.19  | V                 |

| R <sub>VINP</sub>      | VINP Resistance                                                    | VINP = 0                                          | -    | 900  | -     | Ω                 |

| ERROR AMPL             | IFIERS                                                             |                                                   |      |      | •     | •                 |

| V <sub>IO</sub>        | Input Offset Voltage<br>(VREG - VINP)                              | I <sub>VCMP</sub> = 0mA                           | -    | -    | 10    | mV                |

| R <sub>IN</sub> VREG   | Input Resistance to GND                                            | VREG = 5.1V                                       | -    | 56   | -     | kΩ                |

| g <sub>m</sub> (VREG)  | VREG Transconductance I <sub>VCMP</sub> /(VREG - VINP)             | VCMP = 1V to 8V, SFST = 11V                       | 15   | 30   | 50    | mS                |

| g <sub>m</sub> (SFST)  | SFST Transconductance I <sub>VCMP</sub> /(VREG - SFST)             | V <sub>SFST</sub> < 4.9V                          | 0.8  | -    | 6     | mS                |

| I <sub>VCMP</sub>      | Maximum Source Current                                             | VREG = 4.95V, VCMP = 8V                           | -2.5 | -    | -0.75 | mA                |

| I <sub>VCMP</sub>      | Maximum Sink Current                                               | VREG = 5.25V, VCMP = 0.4V                         | 0.75 | -    | 2.5   | mA                |

| OVTH                   | Over-Voltage Threshold                                             | Voltage at VREG for FLTN to be latched            | 6.2  | -    | 6.7   | V                 |

| CLOCK                  |                                                                    |                                                   | •    | •    | •     |                   |

| fq                     | Internal Clock Frequency                                           | SLCT = 0V, V <sub>DDD</sub> = 12V                 | 0.9  | 1.0  | 1.1   | MHz               |

| V <sub>TH</sub> CKIN   | External Clock Input Threshold Voltages                            | SLCT = 12V                                        | 33   | -    | 66    | %V <sub>DDD</sub> |

| DMOS TRANS             | SISTORS                                                            | •                                                 |      |      | •     |                   |

| r <sub>DS(on)</sub>    | Drain-Source On-State<br>Resistance                                | I Drain = 5A, T <sub>J</sub> = +25 <sup>o</sup> C | -    | -    | 0.13  | Ω                 |

| I <sub>DSS</sub>       | Drain-Source Leakage Current                                       | Drain to Source Voltage = 60V                     | -    | 1    | 100   | μА                |

| CURRENT CO             | NTROLLED PWM                                                       | •                                                 |      |      |       |                   |

| V <sub>IO</sub>   VCMP | Buffer Offset Voltage (VCMP - VIRFO)                               | IRFO = 0mA to -5mA,<br>VCMP = 0.2V to 7.6V        | -    | -    | 125   | mV                |

| V <sub>TH</sub> IRFO   | Voltage at IRFO that disables PWM. This is due to low load current |                                                   | 100  | -    | 270   | mV                |

## HIP5060

# **Electrical Specifications** V+ = 36V, $T_J = 0^{\circ}C$ to +110°C; Unless Otherwise Specified (Continued)

| SYMBOL                   | PARAMETER                                                                                      | TEST CONDITIONS                               | MIN  | TYP  | MAX  | UNITS |

|--------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------|------|------|------|-------|

| CURRENT CO               | NTROLLED PWM (Continued)                                                                       |                                               | •    |      | •    |       |

| I <sub>TH</sub> IRFO     | Voltage at IRFO to enable SHRT output current. This is due to Regulator Over Current Condition |                                               | 7.4  | -    | 8.0  | V     |

| I <sub>SHRT</sub>        | SHRT Output Current, During<br>Over-Current                                                    | V <sub>IRFO</sub> = 8.1V                      | -37  | -    | -17  | μА    |

| V <sub>TH</sub> SHRT     | Threshold voltage on SHRT to set FLTN latch                                                    |                                               | 4    | 6    | 8    | V     |

| I <sub>GAIN</sub>        | I <sub>PEAK</sub> (DMOS <sub>DRAIN</sub> )/I <sub>IRFI</sub>                                   | ΔI (DMOS <sub>DRAIN</sub> )/Δt = 1A/ms        | 3.8  | -    | 4.9  | A/mA  |

| R <sub>IRFI</sub>        | IRFI Resistance to GND                                                                         | I <sub>IRFI</sub> = 2mA                       | 150  | -    | 360  | Ω     |

| t <sub>RS</sub> (Note 1) | Current Comparator Response Time                                                               | $\Delta I (DMOS_{DRAIN})/\Delta t > 1A/\mu s$ | -    | 30   | -    | ns    |

| MCPW (Note<br>1)         | Minimum Controllable Pulse<br>Width                                                            |                                               | 25   | 50   | 100  | ns    |

| MCPI<br>(Note 1)         | Minimum Controllable DMOS<br>Peak Current                                                      |                                               | 200  | 400  | 800  | mA    |

| START-UP                 | •                                                                                              |                                               | •    |      | •    |       |

| V+                       | Rising V+ Power-On Reset<br>Voltage                                                            |                                               | 22   | -    | 27   | V     |

| V+                       | Falling V+ Power-Off Set<br>Voltage                                                            |                                               | -    | 15   | -    | V     |

| V+                       | V+ Power-On Hysteresis                                                                         |                                               | 9    | -    | 12   | V     |

| V <sub>TH</sub> PSEN     | Voltage at PSEN to Enable Supply                                                               |                                               | 0.8  | -    | 2.0  | V     |

| rpsen                    | Internal Pull-Up Resistance, to 5.1V                                                           |                                               | -    | 20   | -    | ΚΩ    |

| I <sub>SFST</sub>        | Soft-Start Charging Current                                                                    | V <sub>SFST</sub> = 0V to 10V                 | -1.0 | -0.7 | -0.4 | μΑ    |

| I <sub>PSOK</sub>        | PSOK High-State Leakage<br>Current                                                             | SFST = 0V, PSOK = 12V                         | -1   | -    | 1    | μА    |

| V <sub>PSOK</sub>        | PSOK Low-State Voltage                                                                         | SFST = 11V, I <sub>PSOK</sub> = 1mA           | -    | -    | 0.4  | V     |

| V <sub>TH</sub> SFST     | PSOK Threshold, Rising V <sub>SFST</sub>                                                       |                                               | 9.4  | -    | 11   | V     |

| THERMAL MO               | NITOR                                                                                          |                                               | •    | ı    |      | •     |

| TEMP<br>(Note 1)         | Substrate Temperature for<br>Thermal Monitor to Trip                                           | TMON pin open                                 | 105  | -    | 135  | °C    |

#### NOTE:

1. Determined by design, not a measured parameter.

# Pin Descriptions

| A current                                           |

|-----------------------------------------------------|

| ne current ing to the pe greater urrent will w 20A. |

|                                                     |

|                                                     |

| ply.                                                |

|                                                     |

| currents<br>of seven,                               |

| nal clock.<br>this termi-<br>ad. There              |

| turned to                                           |

|                                                     |

| ors. The<br>MOS                                     |

|                                                     |

|                                                     |

| circuit. By<br>he IC into<br>irs at a               |

| turned to                                           |

|                                                     |

|                                                     |

| icy com-                                            |

| internally                                          |

| This node<br>then over-                             |

| u e n                                               |

# Functional Block Diagram